# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

2007年版

新探究デバイス

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# 訳者まえがき

この文書は International Technology Roadmap for Semiconductors 2007 Edition(国際半導体技術ロードマップ 2007年版)の全訳である。

国際半導体技術ロードマップ(以下 ITRS と表記)は、米国、日本、欧州、韓国、台湾の世界5極の専門家によって編集・作成されている。日本では、半導体技術ロードマップ専門委員会(STRJ)が電子情報技術産業協会(JEITA)内に組織され、日本国内で半導体技術ロードマップについての調査活動を行うとともに、ITRS の編集・作成に貢献している。STRJ 内には 14 のワーキンググループ(WG: Working Group)、2つのタスクフォース(設計タスクフォースと故障解析タスクフォース)、経済性検討小委員会が組織され、半導体集積回路メーカー、半導体製造装置メーカ、材料メーカ、大学、独立行政法人、コンソーシアなどから専門家が集まり、それぞれの専門分野の調査活動を行っている。

ITRS は改版を重ねるごとにページ数が増え、2007年版は英文で約1000ページの文書となった。このような大部の文書を原文で読み通すことは専門家でも多大な労力を要するし、専門家であっても技術分野が少し異なるとITRS を理解することは必ずしも容易でない。STRJ の専門委員がその専門分野に応じてITRS を訳出することで、ITRS をより親しみやすいものにすることができるのではないかと考えている。

なお、ITRS 2005 年版(英語の原書)までは、ウェブ公開とともに、印刷された本としても出版していたが、2007 年版以降、は印刷コストが大きくなってきたこと、ウェブ上で無料公開されている文書の出版版を本の形で有償頒布しても需要が限られることなどのため、印刷物の形での出版を断念し、ウェブ公開のみとなった。ITRS の読者の皆様にはご不便をおかけするが、ご理解願いたい。

訳文の作成は、STRJ 委員が分担してこれにあたり、JEITA の STRJ 担当事務局が全体の取りまとめを行った。訳語については、できる限り統一するように努めたが、なお、統一が取れていないところもある。また、訳者によって、文体が異なるところもある。ITRS の原文自体も多くの専門家による分担執筆であり、そもそも原文の文体も一定していないことも、ご理解いただきたい。誤訳、誤字脱字などが無いよう、細心の注意をしているが、短期間のうちに訳文を作成しているため、なお間違いが含まれていると思う。また、翻訳の過程で原文のニュアンスが変化してしまうこともある。訳文についてお気づきの点や、ITRS についてのご批判、ご意見などを事務局まで連絡いただければありがたい。

今回の訳出にあたっては、ITRS の本文の部分のみとし、ITRS 内の図や表の内部の英文は訳さないでそのまま掲載することとした。Executive Summary の冒頭の謝辞(Acknowledgments)に、ITRS の編集にかかわった方々の氏名が書かれているが、ここも訳出せず、原文のままの表記とした。原文中の略語については、できるかぎり、初出の際に、「ITRS(International Technology Roadmap for Semiconductors)」のように()内に原義を示すようにした。英文の略号をそのまま使わないで技術用語を訳出する際、原語を引用したほうが適切と考えられる場合には、「国際半導体技術ロードマップ (ITRS: International Technology Roadmap for Semiconductors、以下 ITRS と表記)」「国際半導体技術ロードマップ (International Technology Roadmap for Semiconductors)」のように和訳の後に()内に原語やそれに対応する略語を表示した。本書の巻末に用語集(Glossary)も参照されたい。原文の括弧()があってそれを訳するために括弧を使った場合もあるが、前後の文脈の関係で判別できると思う。また訳注は「【訳者注:この部分は訳者の注釈であることを示す】」のように【】内に表記した。また[]内の部分は、訳者が原文にない言葉をおぎなった部分であることを示している。訳文は厳密な逐語訳ではなく、日本語として読んで意味が通りやすいように意訳している。ITRS のウェブ版ではハイパーリンクが埋め込まれているが、今回の日本語版ではハイパーリンクは原則として削除した。読者の皆様には不便をおかけするが、ご理解いただけば幸いである。

今回の日本語訳全体の編集は全体のページ数が膨大であるため、大変な作業となってしまいました。 編集作業を担当いただいた、JEITA内 SRTJ 事務局の古川昇さん、恩田豊さん、近藤美智さん、明石理 香さんに大変お世話になりました。厚くお礼申し上げます。 より多くの方に ITRS をご活用いただきたいとの思いから、今回の翻訳作業を進めました。今後とも ITRS と STRJ へのご理解とご支援をよろしくお願い申し上げます。

2008年5月 訳者一同を代表して

電子情報技術産業協会(JEITA)半導体部会 半導体技術ロードマップ専門委員会(STRJ) 委員長 石内 秀美 (株式会社 東芝)

# 版権について

# ORIGINAL (ENGLISH VERSION) COPYRIGHT © 2007 SEMICONDUCTOR INDUSTRY ASSOCIATION

All rights reserved

ITRS • 2706 Montopolis Drive • Austin, Texas 78741 • 512.356.7687 • http://public.itrs.net

Japanese translation by the JEITA, Japan Electronics and Information Technology Industries Association under the

license of the Semiconductor Industry Association

#### - 引用する場合の注意-

原文(英語版)から引用する場合: 2007 ITRS page XX, Figure(Table) YY この和訳から引用する場合: 2007 ITRS JEITA 和訳 XX 頁,図(表)YY と明記してください。

#### 問合せ先:

社団法人 電子情報技術産業協会 半導体技術ロードマップ専門委員会 事務局 Tel: 03-5275-7258 mailto: roadmap@jeita.or.jp

# TABLE OF CONTENTS

| スコーフ | r . | 1 |

|------|-----|---|

| 73-  | ,   | 1 |

| 困難な技術課題 (Difficult Challenges)                   | 2              |

|--------------------------------------------------|----------------|

| 序章                                               |                |

| デバイス技術                                           | 2              |

| 材料技術                                             |                |

| ナノ情報処理の分類 (Nano-information Processing Taxonomy) |                |

| 新探究デバイス 5                                        |                |

| メモリデバイス                                          | <u>.</u>       |

| メモリの分類                                           | 6              |

| メモリデバイス ― 掲載したメモリの定義と議論                          | 13             |

| ロジック及び代替え情報処理デバイス                                | 17             |

| ロジックデバイス                                         |                |

| ロジックデバイス―表に加えるための定義と議論                           |                |

| 代替え情報処理デバイス                                      |                |

| 代替え情報処理デバイス―表の欄の定義と議論                            | 25             |

| 新探究アーキテクチャ                                       | 30             |

| はじめに                                             | 30             |

| CMOS「メニーコア」アーキテクチャのトレンド                          | 30             |

| 「ヘテロマルチコア」アーキテクチャ                                | 31             |

| 新探究デバイスが利用される可能性のあるアーキテクチャ                       | 34             |

| 新探究メモリ・論理デバイスー重要な評価                              | 36             |

| 序論                                               | 36             |

| CMOSを越える技術                                       | 36             |

| 技術要求と妥当性基準                                       | 36             |

| 電荷ベースのナノスケールデバイス                                 |                |

| 新規コンピュータ状態変数ナノスケールデバイス                           |                |

| メモリとロジックデバイスの潜在的性能の評価                            |                |

| 計測技術                                             |                |

| 結果                                               | 40             |

| 基本的な指導原理—「CMOSを超える技術」による情報処理                     | 51             |

| はじめに                                             | 51             |

| 指導原理                                             | 51             |

| 電荷以外の計算状態変数                                      | 5 <sup>2</sup> |

| 非熱平衡状態システム                                       |                |

| 新しいエネルギー伝達相互作用                                   |                |

| ナノスケールの熱伝導制御                                     |                |

| サブリソグラフィック作製プロセス                                 |                |

| エマージングアーキテクチャ                                    | 51             |

Endnotes 52

# LIST OF FIGURES

| Figure ERD1                   | A Taxonomy for Emerging Research Information Processing Devices              | 5      |

|-------------------------------|------------------------------------------------------------------------------|--------|

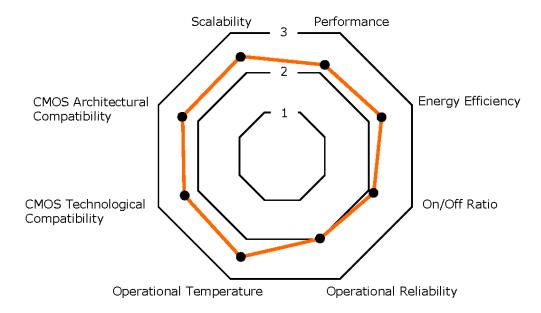

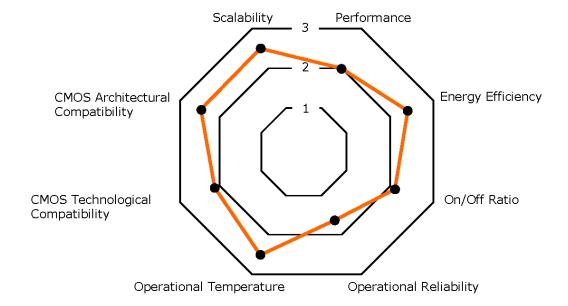

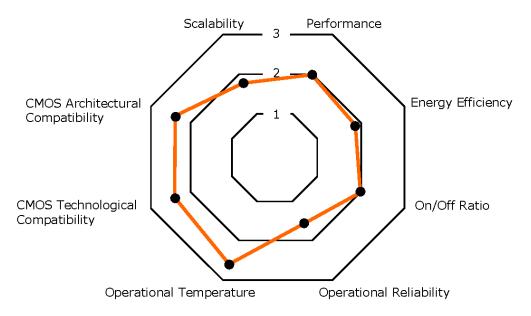

| Figure ERD2a                  | Technology Performance Evaluation for Engineered Tunnel Barrier Memo         | ory.44 |

| Figure ERD2b                  | Technology Performance Evaluation for Fuse/Antifuse Memory                   | 44     |

| Figure ERD2c                  | Technology Performance Evaluation for Nano Mechanical Memory                 | 45     |

| Figure ERD2d                  | Technology Performance Evaluation for Electronic Effects Memory              | 45     |

| Figure ERD2e                  | Technology Performance Evaluation for Ionic Memory                           | 46     |

| Figure ERD2f                  | Technology Performance Evaluation for Ferroelectric FET Memory               | 46     |

| Figure ERD2g                  | Technology Performance Evaluation for Macromolecular Memory                  | 47     |

| Figure ERD2h                  | Technology Performance Evaluation for Molecular Memory                       | 47     |

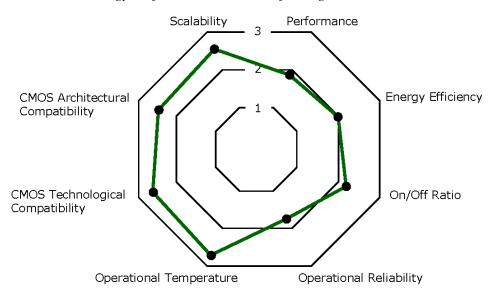

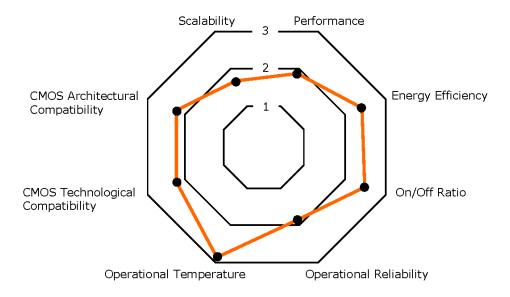

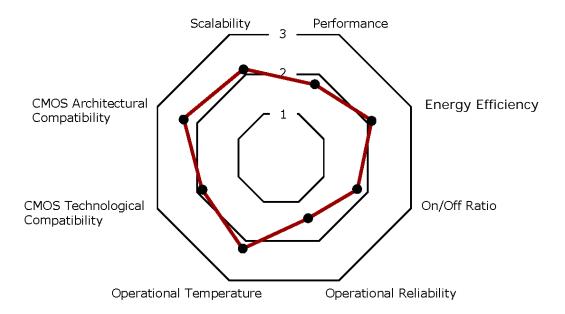

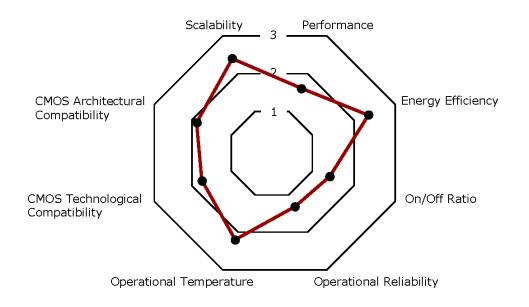

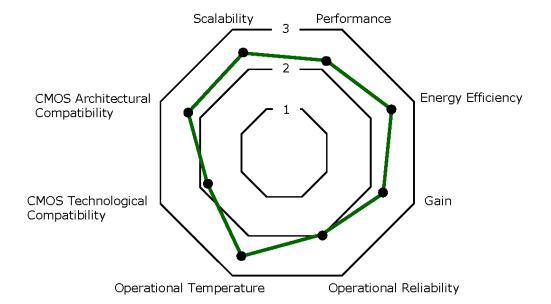

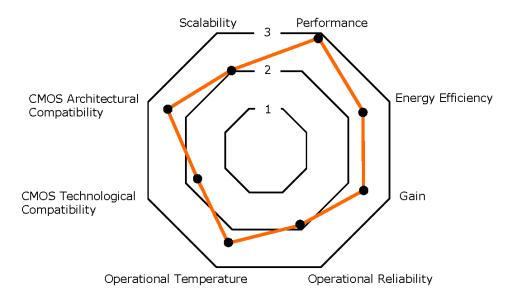

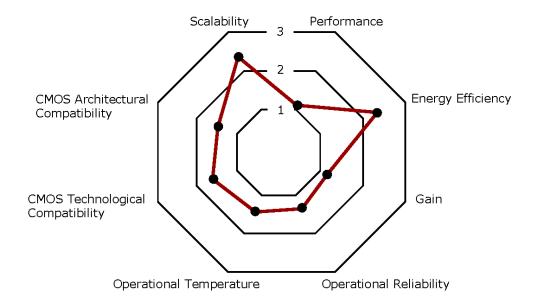

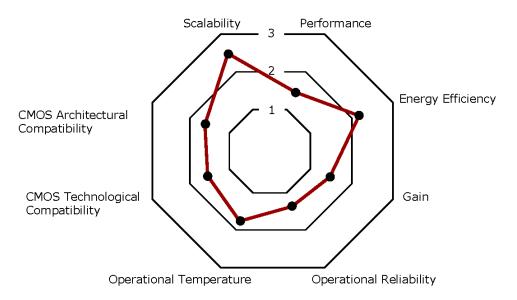

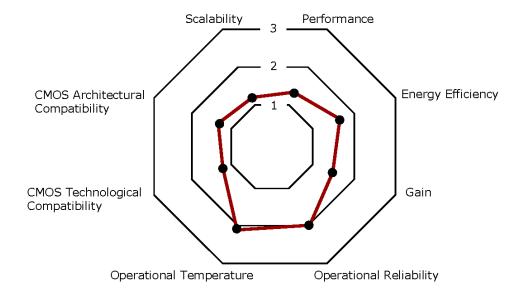

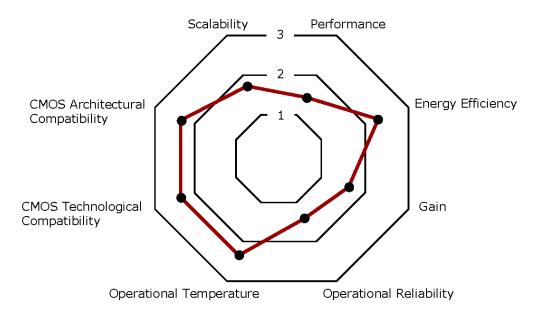

| Figure ERD3a<br>Logic Devices | Technology Performance Evaluation for 1D Structures (CNTs and NWs) 48        |        |

| Figure ERD3b<br>Logic Devices | Technology Performance Evaluation for Channel Replacement Materials 48       |        |

| Figure ERD3c<br>Logic Devices | Technology Performance Evaluation for Single-Electron Transistors 49         |        |

| Figure ERD3d                  | Technology Performance Evaluation for Molecular Logic Devices                | 49     |

| Figure ERD3f                  | Technology Performance Evaluation for Ferromagnetic Logic Devices            | 50     |

| Figure ERD3e                  | Technology Performance Evaluation for Spin Transistors Logic Devices .       | 50     |

| LIST OF TABLES                |                                                                              |        |

| Table ERD1                    | Emerging Research Devices Difficult Challenges                               |        |

| Table ERD2                    | Memory Taxonomy                                                              |        |

| Table ERD3                    | Current Baseline and Prototypical Memory Technologies                        |        |

| Table ERD4                    | Transition Table for Emerging Research Memory Devices                        | 9      |

|                               | Emerging Research Capacitance-based Memory Devices— and Projected Parameters | 10     |

| Table ERD5b  Demonstrated a   | Emerging Research Resistance-based Memory Devices— and Projected Parameters  | 12     |

| Table ERD6                    | Transition Table for Emerging Research Logic Devices                         | 18     |

| Table ERD7a<br>Demonstrated   | Emerging Research Logic Devices— and Projected Parameters                    | 19     |

| Table ERD7b                   | Alternative Information Processing Devices                                   | 25     |

| Table ERD8                    | Emerging Research Architectures                                              | 35     |

| Table ERD9                    | Potential Evaluation for Emerging Research Memory Devices                    | 42     |

| Table ERD10                   | Potential Evaluation for Emerging Research Logic Devices                     | 43     |

|                               |                                                                              |        |

# 新探究素子(ERD, EMERGING RESEARCH DEVICES)

#### スコープ

留まるところを知らない CMOS 微細化に牽引され、情報技術はさまざまな市場において新しい分野に広が り新しい応用技術を可能としてきた。CMOS デバイス寸法の微細化は、少なくともこのロードマップがカバー する期間中は続くであろうし、また CMOS の性能向上あるいはそれと"同等"な向上は、その期間を超えても 続くであろう。極限まで微細化された MOS トランジスタはほぼ理想的な電荷ベースのデバイスである。その 性質を最大限に利用して、CMOS は微細化が終焉を迎えた後も間違いなく情報処理技術のプラットフォー ムであり続けるであろう。CMOS プロセッサコアとヘテロに集積化され非ブール関数による特別な機能を有す る新しい情報処理技術<sup>1</sup>は、現在の応用技術により効率的なソリューションを与え CMOS プラットフォームの 機能スケーリングをさらに広げるであろう。

上記のような可能性があるため、2007 年版の新探究素子(ERD)の章はスコープと内容を拡張することにな った。この章では、メモリ、情報処理・ロジックデバイス、およびナノアーキテクチャのための新しい研究途上 の技術について評価を行う。集積電子機能を実現するための 2 つの異なるアプローチを対象とする。一つ は、これらの新しい技術をヘテロに CMOS プラットフォームに集積することであり、"CMOS の延長"あるいは" 機能の多様化"と呼ぶべきアプローチである。二つ目は、根本的に新しい情報処理あるいは信号処理を発 明するという刺激的ではあるが辟易とするほどの困難へアプローチすることである。このテーマで要求される ことは、新しい材料、プロセス、デバイス、ナノアーキテクチャを通じた新しい情報表現、プロセス、記憶、情報 伝達を発明し利用することである。さらに、2005年版の ERD の章で導入された新探究材料(Emerging Research Materials)の節が拡張されて、一つの章となった。新デバイスに関連する材料研究の課題は、この ERDの章でも纏められているが、新しい新探究材料の章でさらに詳しく取り扱われている。

この章の主な目標は、「極限微細化 CMOS」を本質的に超えて情報処理の機能を拡張する新概念の発明 および研究を促進することである。この目標を達成するには、上で示した 2 つの技術領域を扱わなければな らない - 新技術のヘテロ集積による CMOS プラットフォームの延長と、その後の新しい情報処理パラダイ ムを発明するような新技術とナノアーキテクチャ概念の開発による CMOS プラットフォームの延長である。

意図は2つに分けられる。1つ目は、もし成功すればCMOSを超えてロードマップを延長するようなメモリ、 情報処理デバイス、情報処理ナノアーキテクチャの代替概念を一箇所に集めることである。このようにして、こ こでの議論は新技術候補に対する入口を提供する。2つ目は、これらの新デバイス技術に対して比較および 評価を与えることである。

さらに一つの節においては、極限微細化 CMOS で達成可能な情報処理を本質的に超えるような情報処 理を支配する根本的な原理を提案している。これにより、この章は半導体産業に新探究デバイス技術に関す る見通しを提供するとともに、バルク CMOS と CMOS スケーリングを超えるマイクロエレクトロニクス領域とを 結ぶ架け橋となる。

この章の議論は次の 3 つのカテゴリーに分けられる。1) メモリデバイス、2) 情報処理またはロジックデバイ ス、3) 情報処理ナノアーキテクチャ、である。議論される内容は、その技術の動作原理、利点、課題、成熟度、 現在および将来の性能等に関する詳細である。また、CMOS プラットフォーム技術と集積されるヘテロコアプ ロセッサとして特別な機能を提供する新デバイスやアーキテクチャについても議論した。その目的は、CMOS

<sup>&</sup>lt;sup>1</sup> Information processing refers to the input, transmission, storage, manipulation or processing, and output of data. The scope of the ERD Chapter is restricted to data or information manipulation, transmission, and storage.

プロセッサとの並列アーキテクチャとして動作し現在のシステム機能をより効率的に行ったり新しいシステム機能を実現するような新デバイスの特別な機能を利用したりすることである。これは、ERD の章の短期的な焦点であり、より長期的な焦点はディジタル CMOS を置き換えるような情報処理の代替技術を発見することである。

以前の ERD の章と同様に、この章には遷移表(Transision Table)が掲載されている。遷移表の目的は 2 つある。一つは、2005 年版の表と比べて新たに加わったり除かれたりした技術をわかりやすく示し、その修正の理由を簡単に説明するためである。2 つ目の目的は、重要と考えられるがまだ ERD の表に掲載する基準に届かない技術を明らかにすることである。これらの技術は将来の版ではさらに注目されて説明が増えたり、逆に減ったりするかも知れないので、遷移表と呼ばれる。このようにこの遷移表は、2005 年版から 2007 年版への技術の変化動向を表している。また、この遷移表は 2009 年版で新たに加わるかも知れない新技術を予告し、あるいは将来の含まれるかも知れない技術を追跡するものでもある。最後に、ある新概念がこの章に含まれているとしても、必ずしもその概念を指示したり保証したりするものではない。逆に、この章に含まれなかったとしても、その概念を排除するものではない。

# 困難な技術課題 (DIFFICULT CHALLENGES)

#### 序章

半導体産業は、CMOS 微細化の終焉に向けて、あるいはそれを超えて集積回路技術を発展させるに際して、2種の困難な技術課題に直面している。1つは、その究極の集積度と機能を超えて CMOS を延長することであり、例えば、CMOS プラットフォームに新しい高速、高集積で、低消費電力メモリを含む技術を集積することにより CMOS を延長させることである。もう 1種の課題は、CMOS のみで達成可能な情報処理を本質的に超えて情報処理技術を発展させることであり、これは CMOS を延長する新デバイスやアーキテクチャのアプローチと新しく発明される情報処理プラットフォーム技術とを革新的に組み合わせることにより達成される。困難な技術課題を Table ERD1 に示す。

## デバイス技術

新探究デバイスに関する困難な技術課題は、メモリ技術に関する課題と、情報処理デバイスすなわちロジックデバイスに関する課題に分けられる。課題の一つは、現在のメモリの最良の特徴を併せ持ち、CMOS プロセスと互換性のある作製技術で作られ、現在の SRAM や FLASH の限界を超えて微細化されるような新メモリ技術が必要なことである。このような技術は、スタンドアローンと混載メモリの双方に必要なメモリデバイス作製プロセスを提供することになるであろう。マイクロプロセッサユニット(MPU)がプログラムを実行する性能は、プロセッサとメモリの相互作用によって制限されており、微細化ではこの問題は解決できない。現在の解決策は、MPU のキャッシュメモリの容量を増やすことであり、その結果、MPU チップ上の SRAM の占有面積が増えている。このトレンドにより、正味の情報処理スループットが実際には下がってしまう。半導体メモリは不揮発性でないので、データを記憶する補助回路に加えて(磁気ハードディスクや光 CD などの)アクセスの遅い外部記憶メディアが必要となっている。したがって、電気的にアクセス可能で不揮発性のメモリ、しかも高速で高集積のメモリの開発が、コンピュータアーキテクチャに革命をもたらすことになるかも知れない。このようなメモリの開発は、ナノスケール CMOS で完全に実現されれば、従来の微細化の恩恵を超えてさらなる情報処理スループットの著しい増大をもたらすことになるであろう。

これに関連する課題は、CMOS ロジック技術を 16nm に向けて、あるいは 16nm を超えて性能向上させることである。CMOS の微細化が次の 10 年で緩やかになった場合に性能向上を続ける方法の一つは、ひずみ Si による MOSFET のチャネルを、より高い準バリスティックキャリア速度と高い移動度を有する別の材料に置き換えることである。候補となる材料としては、ひずみ Ge、SiGe、多くの III-V 族化合物半導体、グラフィ

ンなどが挙げられる。シリコン以外の材料をシリコン基板上の MOSFET のチャネルに導入することは、非常 に困難な課題を伴う。これらの課題として挙げられるのは、格子定数が異なるシリコン上に高品質の(すなわ ち無欠陥の)チャネル材料を形成すること、バンドギャップが狭い材料の場合はバンド間トンネル電流を最小 に抑えること、III-V 族半導体や Ge の表面におけるフェルミレベルピニングをなくすこと、チャネル材料上に high-k 絶縁膜材料を形成することなどである。これらの微細 CMOS ゲートにおけるリーク電流や消費電力を 抑制し続けることも課題である。また、これらの新材料を導入しつつ同時にデバイス寸法のばらつきやソース ドレインの不純物による統計的なばらつきを抑制することも大きな課題である。

長期的な課題は、"beyond CMOS"に向けて製造可能な新しい情報処理技術を発明し、それらの応用技 術を特定することである。例えば、新探究デバイスは、CMOS のマルチ CPU と集積して特別な用途をもつプ ロセッサコアを実現するために用いられるかも知れない。これらの特別用途のコアはディジタル CMOS ブロッ クよりはるかに効率的な特別のシステム機能を有するかも知れず、またそれらは CMOS ベースでは達成でき ない独特の新機能をもたらすかも知れない。このような CMOS 微細化の終焉を超えるための解決策は、新 情報処理の基本的要素としてCMOSを置き換える新探究デバイス技術を生み出す可能性がある。

Table ERD1 Emerging Research Devices Difficult Challenges

| Difficult Challenges ≥ 22 nm                                                                             | Summary of Issues and opportunities                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Scale high-speed, dense, embeddable, volatile and non-volatile memory technologies to and beyond 22 nm   | SRAM and FLASH scaling will reach definite limits within the next several years (see PIDS chapter for Difficult Challenges).  These are driving the need for new memory technologies to replace SRAM and FLASH memories.                                                                                                                                                                                                                             |  |  |  |

|                                                                                                          | Identify the most promising technical approach(es) to obtain electrically accessible, high-speed, high-density, low-power, (preferably) embeddable volatile and non-volatile RAM                                                                                                                                                                                                                                                                     |  |  |  |

| Difficult Challenges <22 nm                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Scale CMOS to and beyond the 16 nm technology generation.                                                | Develop new materials to replace silicon as an alternate channel to increase the saturation velocity and maximum drain current in MOSFETs while minimizing leakage currents and power dissipation for technology scaled to 16 nm and beyond. Candidate materials include Ge, SiGe, III-V compound semiconductors, and graphene. Develop 1D (nanowire or nanotube) structures to scale MOSFETs and CMOS gates beyond the 16 nm technology generation. |  |  |  |

|                                                                                                          | Develop means to control the variability of critical dimensions and statistical distributions (e.g., gate length, channel thickness, S/D doping concentrations, etc.)                                                                                                                                                                                                                                                                                |  |  |  |

| Extend ultimately scaled CMOS as a platform technology into new domains of application.                  | Discover and reduce to practice new device technologies and a primitive-level architecture to provide special purpose optimized functional cores heterogeneously integrable with silicon CMOS.                                                                                                                                                                                                                                                       |  |  |  |

| Continue functional scaling of information processing technology substantially beyond that attainable by | Invent and develop a new information processing technology eventually to replace CMOS                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| ultimately scaled CMOS.                                                                                  | Ensure that a new information processing technology is compatible with the new memory technology discussed above; i.e., the logic technology must also provide the access function in a new memory technology.                                                                                                                                                                                                                                       |  |  |  |

|                                                                                                          | Bridge a knowledge gap that exists between materials behaviors and device functions.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

#### 材料技術

新探究材料の最も困難課題は、ナノメートルスケールで高密度の新探究デバイスが正常に動作するよう制御された新材料を提供することである。高密度デバイスの材料特性の制御を向上させるため、材料形成の研究は新しい計測とモデルを用いて行われなければならない。これらの重要な目的は新しい新探究材料の章で扱う。

# ナノ情報処理の分類 (NANO-INFORMATION PROCESSING TAXONOMY)

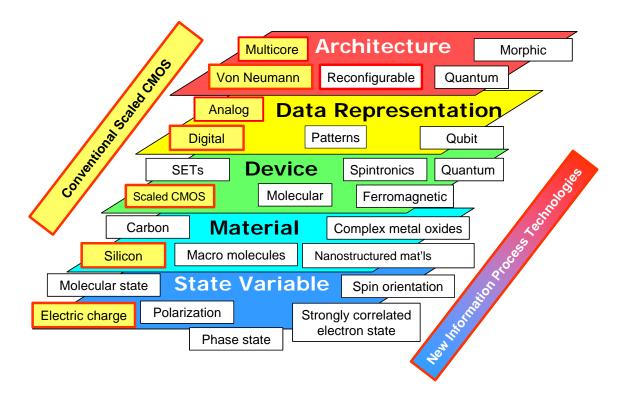

一般に、情報処理によってあるシステム機能を達成するには、いくつかの異なる相互に関連する技術レイ ヤーを必要とする。これらのレイヤーをトップダウンで表示すると、まず最初にくるのは必要なアプリケーション またはシステム機能であり、続いてシステムアーキテクチャ、マイクロまたはナノアーキテクチャ、回路、デバイ ス、材料の順となる。図 ERD1 に示すとおり、この階層構造を逆にボトムアップ的に異なる表し方をすると、最 初にくるのは計算を行うための状態変数によって表される最下層の物理レイヤーであり、最後はナノアーキ テクチャで表される最上層となる。より模式的に表わされたこの図では、汎用的なデバイス・回路レベルの情 報処理に焦点を当てており、情報の最も基本的な単位(例えばビットなど)は計算の状態変数によって表され る。例えば、古代のアバカス(そろばんに似た計算器)では、玉の位置がこれに相当し、CMOS ロジックでは ノード容量における電圧がこれに相当する。デバイスは、この状態変数が2つあるいはそれ以上の離散的な 状態の間を行き来するのを操作する物理的な方法を提供する。デバイスは、ある所望の特性を有する数多く の材料が集まって構成される物理的な構造であり、それは一連の作製プロセスを行うことによって作製される。 データ表現とは、その状態変数をデバイスの集合体によっていかに表現しデータ処理を行うかの方法である。 データ表現の最も良い例は、2値のディジタル表現と連続的なアナログ信号処理である。アーキテクチャのレ イヤーやこの分類法では3つのサブ領域に分けられる:1)計算の実行を可能とする高次レベルの根本機能 を構成するナノアーキテクチャあるいは物理的配列あるいはデバイスの集合体、2)情報が根本機能を用い て処理されるアルゴリズムを記述する計算モデル(例えばロジック、計算、メモリ、セルラ非線形ネットワーク (CNN)など)、および 3) 計算モデルを実行するシステムの構造や機能を記述するシステムレベルのアーキテ クチャ。

Figure ERD1 A Taxonomy for Emerging Research Information Processing Devices

赤枠で囲まれた黄色の部分に書かれている要素は現在の CMOS プラットフォーム技術を表している。計 算の状態変数は電荷でフォンノイマンアーキテクチャを用いており、ディジタルのデータ表現を用いた計算 システムが可能となっている。アナログのデータ表現も現在の CMOS プラットフォーム技術に含まれている。 これらの 5 つのカテゴリーに書かれている他の候補は、互いに組み合わされたり革新的に使われたりするこ とにより、新しく非常にスケーラブルな情報処理のパラダイムを提供する可能性がある。

# 新探究デバイス

# メモリデバイス

この章で取り上げられたメモリ技術は、概ね 2005-2007 年の間に発表された研究成果の中から、現行技術 の限界を打破しうる有力な代替案として選定された代表例である。歴史的には、新規メモリ提案の中から実 用化に結びついた例は極めて希である。現在行われている研究は、種々の基本的なメモリ動作原理の探索 である。これらの動作原理には、誘電体中に孤立保持された電子電荷、強誘電体ゲート絶縁膜の残留分極、 そして、多種多様な現象による抵抗変化が含まれている。表 ERD2 には、既存及び研究中のメモリ技術を、 それぞれの特徴を踏まえつつ、構成要素に応じて4つに分類してある。各メモリ選択肢は、CMOS技術基盤 と不都合なく一体化できることが強く求められている。そのために必要な CMOS 基盤技術の修正、あるいは 混載技術が検討されている。目指す目標の一つは、馴染みのあるシリコンメモリチップと同等の使い勝手を 有するデバイスをエンドユーザーに提供することである。

上記の新規メモリの開発はどれも現状メモリの性能を参考にしているため、主要な動作特性値を、既存の標準的メモリと実用化が始まった新メモリに対して表 ERD3 に示してある。これらの特性値は、各新規探索メモリ技術の現状性能と将来目標値の比較をする上での良いベンチマークとなる。

2007 年版 ITRS に載せた新探索メモリは、いくつかの点で 2005 年版と異なる。この章からはずしたメモリと新たに付け加えたものとを ERD メモリデバイスの変遷表(表 ERD4)にまとめる。変化点は、1) ナノ浮遊ゲート型メモリをはずしたこと、2)絶縁体の抵抗変化利用メモリを以下の 3 つに置き換えたこと、すなわち 3)ヒューズ/反ヒューズ型メモリ、4)イオン移動メモリ、5)電子効果利用メモリであり、最後は、6)ナノメカニカル型メモリを加えたことである。これらの変化の理由と動機も表 ERD4 に述べられている。また、"Emerging Research Memory Devices"の表は、容量型メモリ(表 ERD5a)と抵抗型メモリ(表 ERD5b)の 2 つに分けられ、それぞれ、現状の特性値と将来目標値が示されている。

この章は、表 ERD5a 及び 5b の見出し行に記載されている 8 種類のメモリ技術についてまとめてある。選択にあたっては関連文献の体系的な調査を行い、対象となる研究活動をできるだけ広く網羅するようにした。取り上げられた各メモリ技術は、理解し易くするため、さらにいくつかのグループに分類されている。それらの技術の指標となるパラメータが表中に挙げられている。各パラメータに対し、次の 3 つの観点から性能値が与えられている。すなわち、1) 実用化に必要な最低レベル、2) 計算と初期の実験結果に基づく理論予想性能値、3) 引用文献に報告された最新の実験データである。

表 ERD5a 及び ERD5b の最下段の行には、最近 2 年間に発表された各メモリ技術に関する論文数を載せてある。この数字は、各メモリに対する最近の研究の活発さを表しており、本表に載せるにあたっての選考の指標の一つとなった。これらの表は多くの文献に基づいており、詳細は併記した各参考文献を参照されたい。各表に付記した記述は、各メモリの動作原理に対する簡単な説明と表中には記載しなかった重要事項をまとめたものである。

#### メモリの分類

表 ERD2 には、メモリ技術を分類する一つの簡単な方法が示されている。ここでは、メモリセルを構成する機能要素で分類してある。たとえば、選択トランジスタと容量型記憶ノードから成るお馴染みの DRAM セルは、1T1C 技術として分類される。他の技術、たとえばデータが磁性材料のスピン状態として保存される MRAM は、1T1R 技術と表される。ここで抵抗"R"は、メモリセルの読み出しがセルを流れる電流値の検出によって行われることを表している。この分類法によれば、等価な機能要素数をできるだけ減らしてメモリセルを簡素化(すなわちセル面積を縮小)している傾向が読み取れ、実用的である。メモリ技術開発の初期段階では、メモリセルは一般に複数のトランジスタと複数の記憶ノード(コンデンサや抵抗)から構成される傾向にあるが、開発が進むにつれ構成要素は簡素化され、1T1x の形に落ち着く。望ましくは、データ記憶素子をトランジスタの中に作り込んだ 1T セルとなることが期待される。超高集積のナノエレのメモリアレイにおいては、トランジスタ "T"の代わりに、2 端子の非線形ダイオード型素子が抵抗型メモリ素子を伴って使われるかもしれない。そのような素子は、1D1R 技術と表されよう。

新興のメモリ技術を差異化する重要な特性の一つは、電源 OFF 時にデータを保持できるかどうかということである。不揮発性メモリは、その点で実用上、本質的な優位性を持つ。不揮発度合いは、データ保持時間で評価される。各種揮発性メモリもそれぞれ特有の保持時間を有しており、ミリ秒から(実際には)電源が供給されている間まで様々である。

Table ERD2 Memory Taxonomy

| Cell Element      | Туре                             | Non-volatility | Retention Time |

|-------------------|----------------------------------|----------------|----------------|

|                   |                                  |                |                |

|                   | MRAM                             | Nonvolatile    | > 10 years     |

|                   | Phase change memory              | Nonvolatile    | > 10 years     |

|                   | Polymer memory                   | Nonvolatile    | > years        |

| 1T1R or 1D1R [A]  | Molecular memory                 | Nonvolatile    | > years        |

| TITIK OF IDIK [A] | Nanomechanical memory            | Nonvolatile    | > years        |

|                   | Fuse/antifuse memory             | Nonvolatile    | > years        |

| -<br> -           | Ionic memory                     | Nonvolatile    | > years        |

|                   | Electronic effects memory        | Nonvolatile    | > years        |

| •                 |                                  |                | •              |

| 4740 [A]          | DRAM                             | Volatile       | ~ seconds      |

| 1T1C [A]          | FeRAM [B]                        | Nonvolatile    | > 10 years     |

|                   |                                  |                |                |

|                   | FB DRAM [A]                      | Volatile       | < seconds      |

|                   | Flash memory                     | Nonvolatile    | > 10 years     |

| 47 [4]            | SONOS                            | Nonvolatile    | > 10 years     |

| 1T [A]            | Nano floating gate memory        | Nonvolatile    | > 10 years     |

|                   | Engineered tunnel barrier memory | Nonvolatile    | > 10 years     |

|                   | FeFET memory [A]                 | Nonvolatile    | > years        |

| •                 |                                  |                |                |

| Multiple T [A]    | SRAM                             | Volatile       | large          |

| Multiple T [A]    | STTM [C]                         | Volatile       | small          |

Notes for Table ERD2:

[A] 1T1R—1 transistor—1 resistor 1D1R—1 diode—1 resistor 1T1C—1 transistor—1 capacitor 1T—1 transistor FB DRAM—floating body DRAM FeFET—ferroelectric FET Multiple T—multiple transistor

[C] STTM—scaleable 2-transistor memory. J. H. Yi, W. S. Kim, S. Song, Y. Khang, H.-J. Kim, J. H. Choi, H. H. Lim, N. I. Lee, K. Fujihara, H.-K. Kang, J. T. Moon, and M. Y. Lee. "Scalable Two-transistor Memory (STTM)." IEDM 2001 p. 36.1.1-4.

<sup>[</sup>B] FeRAM—ferroelectric RAM with one ferroelectric transistor and one ferroelectric capacitor

Table ERD3 Current Baseline and Prototypical Memory Technologies

|                             |        | Baseline Technologies |                  |                                                |                               | Pro                           | totypical Te                           | echnologies [                                                 | A]                                                                                 |                                                                     |

|-----------------------------|--------|-----------------------|------------------|------------------------------------------------|-------------------------------|-------------------------------|----------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                             |        | Stand-<br>alone       | Embedded [C]     | SRAM<br>[C]                                    | Floating<br>NOR               | Gate [E]                      | Trapping<br>Charge [G]                 | FeRAM                                                         | MRAM                                                                               | PCM                                                                 |

| Storage Mec                 | hanism |                       | ge on a          | Inter-<br>locked<br>state of<br>logic<br>gates | _                             | n floating                    | Charge<br>trapped in<br>gate insulator | Remnant<br>polarization<br>on a<br>ferroelectric<br>capacitor | Magnetization<br>of<br>ferromagnetic<br>layer                                      | Reversibly<br>changing<br>amorphous<br>and<br>crystalline<br>phases |

| Cell Elemen                 | ts     | 1                     | Г1С              | 6T                                             | 1                             | T                             | 1T                                     | 1T1C                                                          | 1(2)T1R                                                                            | 1T1R                                                                |

| Feature                     | 2007   | 68                    | 90               | 65                                             | 90                            | 90                            | 65                                     | 180                                                           | 90                                                                                 | 65                                                                  |

| size F, nm                  | 2022   | 12                    | 25               | 13                                             | 18                            | 18                            | 10                                     | 65                                                            | 22                                                                                 | 18                                                                  |

| Cell Area                   | 2007   | 6F <sup>2</sup>       | 12F <sup>2</sup> | 140 F <sup>2</sup>                             | 10 F <sup>2</sup>             | 5 F <sup>2</sup>              | 6F <sup>2</sup>                        | 22F <sup>2</sup>                                              | 20F <sup>2</sup>                                                                   | 4.8F <sup>2</sup>                                                   |

| Cell Area                   | 2022   | 6F <sup>2</sup>       | 12F <sup>2</sup> | 140 F <sup>2</sup>                             | 10 F <sup>2</sup>             | 5 F <sup>2</sup>              | 5.5F <sup>2</sup>                      | 12F <sup>2</sup>                                              | 16F <sup>2</sup>                                                                   | 4.7F <sup>2</sup>                                                   |

| Read Time                   | 2007   | <10 ns                | 1 ns             | 0.3 ns                                         | 10 ns                         | 50 ns                         | 14 ns                                  | 45 ns [I]                                                     | 20 ns [M]                                                                          | 60 ns [P]                                                           |

| Keaa Time                   | 2022   | <10 ns                | 0.2 ns           | 70 ps                                          | 2 ns                          | 10 ns                         | 2.5 ns                                 | <20 ns [J]                                                    | <0.5 ns                                                                            | < 60 ns                                                             |

| W/E Time                    | 2007   | <10 ns                | 0.7 ns           | 0.3 ns                                         | 1 μs/<br>10 ms                | 1/0.1ms                       | 20μs/20ms[H]                           | 10 ns [K]                                                     | 20 ns [M]                                                                          | 50/120ns[P]                                                         |

| W/E Time                    | 2022   | <10 ns                | 0.2 ns           | 70 ps                                          | 1 μs/<br>10 ms                | 1 ms/<br>0.1 ms               | ~10µs/10ms                             | 1 ns[J]                                                       | <0.5 ns [N]                                                                        | <50 ns                                                              |

| Retention                   | 2007   | 64 ms                 | 64 ms            | [D]                                            | >10 y                         | > 10 y                        | >10 y                                  | >10 y                                                         | >10 y                                                                              | >10 y                                                               |

| Time                        | 2022   | 64 ms                 | 64 ms            | [D]                                            | >10 y                         | > 10 y                        | >10 y                                  | >10 y                                                         | >10 y                                                                              | >10 y                                                               |

| Write                       | 2007   | >3E16                 | >3E16            | >3E16                                          | >1E5                          | >1E5                          | 1E5                                    | 1E14                                                          | >3E16                                                                              | 1E8                                                                 |

| Cycles                      | 2022   | >3E16                 | >3E16            | >3E16                                          | >1E5                          | >1E5                          | 1E6                                    | >1E16                                                         | >1E16                                                                              | 1E15                                                                |

| Write                       | 2007   | 2.5                   | 2.5              | 1.1                                            | 12                            | 15                            | 7–9                                    | 0.9-3.3                                                       | 1.5 [M]                                                                            | 3 [P]                                                               |

| Operating<br>Voltage<br>(V) | 2022   | 1.5                   | 1.5              | 0.7                                            | 12                            | 15                            | 4-6                                    | 0.7–1                                                         | <1.5                                                                               | <3                                                                  |

| Read                        | 2007   | 2                     | 2                | 1.1                                            | 2                             | 2                             | 1.6                                    | 0.9–3.3                                                       | 1.5 [M]                                                                            | 3                                                                   |

| Operating<br>Voltage<br>(V) | 2022   | 1.5                   | 1.5              | 0.7                                            | 1.1                           | 1.1                           | 1.1                                    | 0.7–1                                                         | <1.8                                                                               | <3                                                                  |

| Write                       | 2007   | 5E-15<br>[B]          | 5E-15            | 7E-16                                          | >1E-14<br>[F]                 | >1E-14<br>[F]                 | 1E-13 [H]                              | 3E-14 [L]                                                     | 7E-11 [A]                                                                          | 5E-12 [Q]                                                           |

| Energy<br>(J/bit)           | 2022   | 2E-15<br>[B]          | 2E-15            | 2E-17                                          | >1E-15<br>[F]                 | >1E-15<br>[F]                 | >1E-15                                 | 5E-15 [L]                                                     | 2E-11 [A]                                                                          | <1E-13 [Q]                                                          |

| Comments                    |        |                       |                  |                                                | Multiple-<br>bit<br>potential | Multiple-<br>bit<br>potential | Multiple-bit<br>potential              | Destructive read-out                                          | Spin-polarized Write has a potential to lower Write current density and energy [O] | Multiple-bit<br>potential                                           |

Notes for Table ERD3:

- [A] 2007 ITRS PIDS chapter.

- [B] Estimated as  $E\sim0.5*CV^2$  for C=25fF,  $V_c=0.65$  Volts (in 2007) and  $V_c=0.35$  Volts in 2022 (energy to refresh is not included).

- [C] See the Embedded Memory Requirements table in the System Drivers chapter.

- [D] SRAM memory state is preserved so long as voltage is applied.

- [E] Embedded applications (see the Embedded Memory Requirements table in the System Drivers chapter).

- $\label{lem:condition} \textit{[F] Lower bound for Fowler Nordheim write/erase}.$

- [G] Trapping charge memories in PIDS chapter include SONOS, and a number of engineered barrier concepts, some of which are described in Table ERD5a.

- [H] J-Y. Wu et al. "A Single-Sided PHINES SONOS Memory Featuring High-Speed And Low-Power Applications." IEEE Electr. Dev. Lett. 27 (2006) 127.

- [I] K. R. Udayakumar et al. "Full-Bit Functional, High-Density 8 Mbit One Transistor-One Capacitor Ferroelectric Random Access Memory Embedded Within A Low-Power 130 nm Logic Process." Jap. J. Appl. Phys. 46 (2007) 2180-2183.

- [J] "Nanoelectronics and Information Technology." Ed. Rainer Waser. Wiley-VCH, 2003, 568-569.

- [K] H. Kohlstedt et al. "Current Status And Challenges Of Ferroelectric Memory Devices." Microelectronic Eng. 80 (2005) 296-304.

- [L] Estimated as  $E \sim 0.5 * q *A *V$  for  $q = 10.9 \ \mu C/cm^2$ ,  $A = 0.33 \ \mu m^2$ ,  $V_c = 1.5 \ Volts$  (in 2007) and  $q = 30 \ \mu C/cm^2$ ,  $A = 0.069 \ \mu m^2$ .  $V_c = 0.7 \ Volts$  (in 2022).

- [M] N. Sakimura et. al. "MRAM Cell Technology For Over 500-MHz SOC." IEEE J. Solid-State Circ. 42 (2007) 830-838.

[N] H. W. Schumacher. "Ballistic bit addressing in a magnetic memory cell array." Appl. Phys. Lett. v. 87, no. 4 (2005) 42504.

[O] Y. Jiang, T. Nozaki, S. Abe, T. Ochiai, A. Hirohata, N. Tezuka, K. Inomata. "Substantial Reduction Of Critical Current For Magnetization Switching In An Exchange-Biased Spin Valve." Nature Materials, v. 3, June 2004, 361-364.

[P] W. Y. Cho, B-H Cho, B-G. Choi, H-R Oh, S. Kang, K-S. Kim, K-H. Kim, D-E. Kim, C-K. Kwak, H-G. Byun, Y. Hwang, S. J. Ahn, G-H. Koh, G. Jeong, H. Jeong, and K. Kim. "A 0.18-µm 3.0-V 64-Mb Nonvolatile Phase-Transition Random Access Memory (PRAM)." IEEE J. Solid-State Circuits v. 40, no. 1 (2005) 291-300.

[Q] Estimated as  $E \sim 0.5 * I^2 R^2 t_w$  for  $I = 235 \mu A$ , R = 3.54E3 Ohm,  $t_w = 50$  ns (in 2007) and  $I = 13 \mu A$ , R = 3.54E4 Ohm, < 50 ns (in 2022).

Table ERD4 Transition Table for Emerging Research Memory Devices

|                                       | IN/OUT (Table ERD5) | Reason for IN/OUT                                                                       | Comment                                                                                                 |

|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Nanofloating Gate Memory              | оит                 | Natural evolution of FG FLASH No major research issues Became a prototypical technology | ERD recommends to include<br>NFLG memory in PIDS<br>(Not included in 2007PIDS<br>chapter)               |

| Insulator Resistance Change<br>Memory | оит                 | Replaced by three new memory categories (see immediately below)                         | This memory category included several different memory types based on different mechanisms of operation |

| Fuse/Antifuse Memory                  | IN                  | Replacement for the Insulator<br>Resistance Change memory                               |                                                                                                         |

| Ionic Memory                          | IN                  | Replacement for the Insulator<br>Resistance Change memory                               |                                                                                                         |

| Electronic Effects Memory             | IN                  | Replacement for the Insulator<br>Resistance Change memory                               |                                                                                                         |

| Nanomechanical Memory                 | IN                  | New device concept, promising characteristics, several recent publications              |                                                                                                         |

Table ERD5a Emerging Research Capacitance-based Memory Devices— Demonstrated and Projected Parameters

|                             |                  | Engineered tunnel barrier memory             | Ferroelectric FET memory                                |  |

|-----------------------------|------------------|----------------------------------------------|---------------------------------------------------------|--|

| Storage Mechanism           |                  | Charge on floating gate                      | Remnant polarization on a ferroelectric gate dielectric |  |

| Cell Elements               |                  | 1T                                           | 1T                                                      |  |

| Device Types                |                  | FG FET with graded/multilayer gate insulator | FET with FE gate insulator                              |  |

|                             | Minimum required | <65 nm                                       | <65 nm                                                  |  |

| Feature size F              | Best projected   | 10 nm [A]                                    | 22 nm [I]                                               |  |

|                             | Demonstrated     | 130/90 nm [B]                                | ~2 µm [J]                                               |  |

|                             | Minimum required | 10 F <sup>2</sup>                            | $8F^2/4F^2$ [F]                                         |  |

| Cell Area                   | Best projected   | 8F <sup>2</sup> /4F <sup>2</sup> [A, F]      | $8F^2/4F^2$ [F]                                         |  |

|                             | Demonstrated     | 6F <sup>2</sup> [B], 4F <sup>2</sup> [C]     | Data not available                                      |  |

|                             | Minimum required | <15 ns                                       | <15 ns                                                  |  |

| Read Time                   | Best projected   | 2.5 ns                                       | 2.5 ns                                                  |  |

|                             | Demonstrated     | 20 ns [D]                                    | 20 ns [H]                                               |  |

| W/E time                    | Minimum required | 1 μs/10 ms                                   | Application dependent                                   |  |

|                             | Best projected   | 1 ns @ 9V[A]                                 | 2.5 ns [B]                                              |  |

|                             | Demonstrated     | ~1 μs @11V [B]                               | 20 ns [K]                                               |  |

|                             | Minimum required | >10 y                                        | >10 y                                                   |  |

| Retention Time              | Best projected   | >10 y                                        | >1 y                                                    |  |

|                             | Demonstrated     | >10 y [B]                                    | >30 days [L, M]                                         |  |

|                             | Minimum required | >1E5                                         | >1E5                                                    |  |

| Write Cycles                | Best projected   | >3E16                                        | >3E16                                                   |  |

|                             | Demonstrated     | 1E5 [G]                                      | 1E12                                                    |  |

|                             | Minimum required | Application dependent                        | Application dependent                                   |  |

| Write Operating Voltage (V) | Best projected   | >3 V [E]                                     | <0.9 V [I]                                              |  |

| (V)                         | Demonstrated     | 6.5 [B]                                      | ±6                                                      |  |

|                             | Minimum required | 2.5                                          | 2.5                                                     |  |

| Read Operating Voltage      | Best projected   | 0.7                                          | 0.7                                                     |  |

| (V)                         | Demonstrated     | 2.5 [D]                                      | 2.5 [D]                                                 |  |

|                             | Minimum required | Application dependent                        | Application dependent                                   |  |

| Write Energy (J/Bit)        | Best projected   | >1E-15                                       | 2E-15 [N]                                               |  |

|                             | Demonstrated     | Data not available                           | Data not available                                      |  |

| Comments                    |                  | Potential for multi-bit/cell storage         | Potential for non-destructive readout                   |  |

| Research activity [O]       |                  | 25                                           | 48                                                      |  |

Notes for Table ERD5a:

- [A] K. K. Likharev. "Riding the crest of a new wave in memory." IEEE Circ. & Dev. v. 16, no. 4 (2000) 16-21.

- [B] P. Blomme; J. De Vos; A. Akheyar; L. Haspeslagh; J. Van Houdt; K. De Meyer. "Scalable Floating Gate Flash Memory Cell With Engineered Tunnel Dielectric and High-K (Al2O3) Interpoly Dielectric." Non-Volatile Semiconductor Memory Workshop, 2006. IEEE NVSMW 2006: 52 – 53.

- [C] J. De Vos, L. Haspeslagh, M. Demand, K. Devriendt, D. Wellekens, S.Beckx, and J. Van Houdt. "A scalable Stacked Gate NOR/NAND Flash Technology compatible with high-k and metal gates for sub 45 nm generations." Proc. ICICDT, pp. 21-24, 2006.

- [D] Based on floating gate and SONOS data (see Table ERD3). The read voltage and read time of all 1T memory devices are expected to be similar.

- [E] Based on minimum barrier height of 1.5 eV for nonvolatile charge retention.

- [F] 4F2 is for NAND or multiple bit storage, see e.g. Y Tabuchi, S. Hasegawa, T. Tamura, H. Hoko, K. Kato, Y. Arimoto, H. Ishiwara. "Multi-bit programming for 1T-FeRAM by local polarization method." 2005 SSDM, pp. 1038-1039.

- [G] Blomme, P., Van Houdt, J., Kristin De Meyer, "Write/erase cycling endurance of memory cells with SiO<sub>2</sub>//HfO<sub>2</sub>/ tunnel dielectric." IEEE Tran. Device and Materials Reliability, V 4 (2004): 345 – 352.

- [H] H. Ishiwara. "Application of Bismuth-layered perovskite thin films to FET-type ferroelectric memories." Integrated Ferroelectrics 79 (2006) 3-13. [1] Fitsilis M, Mustafa Y, Waser R, Scaling the ferroelectric field effect transistor, Integrated Ferroelectrics 70: 29-44 2005.

- [J]] M. Takashashi and S. Sakai. "Self-aligned-gate Metal/Ferroelectric/Insulator/Semiconductor field-effect transistors with long memory retention." Jap. J. Appl. Phys. 44 (2005) L800-L802.

- [K] K. Aizawa, B-E. park, Y. Kawashima, K. Takabashi, and H. Ishiwara. "Impact of HfO2 buffer layers on data retention characteristics of ferroelectric-gate field-effect transistors." Appl. Phys. Lett. 85 (2004) 3199.

- [L] K. Takahashi, K. Aizawa, B.-E. Park, and H. Ishiwara. "Thirty-days-long Data Retention in Ferroelectric-gate Ferroelectric Effect Transistor with HfO2 Buffer Layers." Jap. J. Appl. Phys 44 (2005) 6218-6220.

- [M] M. Takahashi and S. Sakai. "Self-aligned-gate Metal/Ferroelectric/Insulator transistors with long memory retention." Jap. J. Appl. Phys. 44 (2005) L800-L802.

- [N] Calculated based on the parameters of scaled ferroelectric capacitor projected in Ref. [I].

- [O] The number of referred articles in technical journals that appeared in the Science Citation Index database for 7/1/2005–7/1/2007.

Table ERD5b Emerging Research Resistance-based Memory Devices— Demonstrated and Projected Parameters

|                        |                | Nanomechanical<br>Memory                                              | Fuse/Antifuse<br>Memory             | Ionic Memory                                                                                                              | Electronic Effects<br>Memory                                                 | Macromolecular<br>Memory | Molecular Memories                             |

|------------------------|----------------|-----------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------|------------------------------------------------|

| Storage Mechanism      |                | Electrostatically-<br>controlled<br>mechanical switch                 | Multiple<br>mechanisms              | Ion transport and redox reaction                                                                                          | Multiple mechanisms                                                          | Multiple<br>mechanisms   | Not known                                      |

| Cell Elements          |                | 1T1R or 1D1R                                                          | 1T1R or 1D1R                        | 1T1R or 1D1R                                                                                                              | 1T1R or 1D1R                                                                 | 1T1R or 1D1R             | 1T1R or 1D1R                                   |

| Device Types           |                | 1) nanobridge/<br>cantilever<br>2) telescoping CNT<br>3) Nanoparticle | M -I-M (e.g.,<br>Pt/NiO/Pt)         | cation migration     anion migration                                                                                      | Charge trapping     Mott transition     FE barrier effects                   | M-I-M (nc)-I-M           | Bi-stable switch                               |

|                        | Min. required  | <65 nm                                                                | <65 nm                              | <65 nm                                                                                                                    | <65 nm                                                                       | <65 nm                   | <65 nm                                         |

| Feature size F         | Best projected | 5-10 nm [B]                                                           | 5-10 nm                             | 5-10 nm                                                                                                                   | 5-10 nm                                                                      | 5-10 nm                  | 5 nm [U]                                       |

| Cell Area  I Read Time | Demonstrated   | 180 nm [A]                                                            | 180 nm [E]                          | 90 nm [G]                                                                                                                 | 1 μm [L]                                                                     | 250 nm [R]               | 30 nm [AB]                                     |

|                        | Min. required  | 10F <sup>2</sup>                                                      | 10 F <sup>2</sup>                   | 10 F <sup>2</sup>                                                                                                         | 10 F <sup>2</sup>                                                            | 10 F <sup>2</sup>        | 10 F <sup>2</sup>                              |

| Cell Area              | Best projected | 5F <sup>2</sup>                                                       | 8/5F <sup>2</sup> [H]               | 8/5F <sup>2</sup> [H]                                                                                                     | 8/5F <sup>2</sup> [H]                                                        | 8/5F <sup>2</sup> [H]    | 5F <sup>2</sup>                                |

|                        | Demonstrated   | Data not available                                                    | Data not available                  | 8F <sup>2</sup> [G]                                                                                                       | Data not available                                                           | Data not available       | Data not available                             |

|                        | Min. required  | <15 ns                                                                | <15 ns                              | <15 ns                                                                                                                    | <15 ns                                                                       | <15 ns                   | <15 ns                                         |

| Read Time              | Best projected | <3 ns                                                                 | <10 ns                              | <10 ns                                                                                                                    | <10 ns                                                                       | <10 ns                   | <10 ns [U]                                     |

|                        | Demonstrated   | 3 ns [C]                                                              | Data not available                  | <50 ns [G]                                                                                                                | Data not available                                                           | ~10 ns [S]               | Data not available                             |

| Min. required          |                | Application dependent                                                 | Application dependent               | Application dependent                                                                                                     | Α.                                                                           |                          | Application dependent                          |

| W/E time               | Best projected | <1 ns [A,B]                                                           | <10 ns                              | <20 ns [P]                                                                                                                | <20 ns [M]                                                                   | <10 ns                   | <40 ns [U]                                     |

|                        | Demonstrated   | 3 ns [C]                                                              | 10 ns/5 μs [E]                      | <50 ns [G]                                                                                                                | 100 ns [M]                                                                   | 10 ns [S]                | 0.2 s [V]                                      |

|                        | Min. required  | >10 y                                                                 | >10 y                               | >10 y                                                                                                                     | >10 y                                                                        | >10 y                    | >10 y                                          |

| Retention Time         | Best projected | >10 y                                                                 | >10 y                               | >10 y                                                                                                                     | >10 y Not known                                                              |                          | Not known                                      |

|                        | Demonstrated   | ~days [A]                                                             | >8 months [E]                       | >10 y [K]                                                                                                                 | 1 y [N]                                                                      | 6 month [Y]              | 2 months [X]                                   |

|                        | Min. required  | >1E5                                                                  | >1E5                                | >1E5                                                                                                                      | >1E5                                                                         | >1E5                     | >1E5                                           |

| Write Cycles           | Best projected | >3E16                                                                 | >3E16                               | >3E16                                                                                                                     | >3E16                                                                        | >3E16                    | >3E16                                          |

|                        | Demonstrated   | >1E9 [A]                                                              | >1E6 [E]                            | >1E6 [G]                                                                                                                  | >1E3 [O]                                                                     | >1E6 [S]                 | >2E3 [W]                                       |

| Write operating        | Min. required  | Application dependent                                                 | Application dependent               | Application dependent                                                                                                     | Application dependent                                                        | Application dependent    | Application dependent                          |

| voltage (V)            | Best projected | Not known [D]                                                         | 0.5/1                               | <0.5 V [Q]                                                                                                                | <3 V                                                                         | <1 V [R]                 | 80 mV[Y]]                                      |

|                        | Demonstrated   | 1.5 V [A]                                                             | 0.5/1 [E]                           | +0.6/-0.2 V [G]                                                                                                           | 3-5 V [L,M]                                                                  | ~±2 [S]                  | ~±1.5 V [W]                                    |

| Read operating         | Min. required  | 2.5                                                                   | 2.5                                 | 2.5                                                                                                                       | 2.5                                                                          | 2.5                      | 2.5                                            |

| voltage (V)            | Best projected | 0.7                                                                   | <0.5                                | <0.2 V [Q]                                                                                                                | 0.7                                                                          | 0.7                      | 0.3 [U]                                        |

| romage (1)             | Demonstrated   | 1.5 V [A]                                                             | 0.4 [E]                             | 0.15 V[G]                                                                                                                 | 0.7 V [L]                                                                    | 1 V [S]                  | 0.5 V [W]                                      |

| Write energy           | Min. required  | Application dependent                                                 | Application dependent               | Application dependent                                                                                                     | Application dependent                                                        | Application dependent    | Application dependent                          |

| (J/bit)                | Best projected | Not known [D]                                                         | Not known                           | 1E-15 [J]                                                                                                                 | <1E-10                                                                       | Not known                | 2E-19 [Y]                                      |

|                        | Demonstrated   | Data not available                                                    | 1E-12 [F]                           | 5E-14 [I]                                                                                                                 | 1E- 9 [P]                                                                    | 1E-13 [T]                | Data not available                             |

| Comments               |                | Inverse voltage<br>scaling presents a<br>problem                      | Potential for multi-<br>bit storage | 2 Mbit prototype chip<br>demonstrated [G]<br>Potential for multi-bit<br>storage<br>Low read voltage<br>presents a problem | Potential for multi-bit<br>storage<br>Low read voltage<br>presents a problem |                          | 160 Kbit prototype<br>chip demonstrated<br>[V] |

| Research activity      | [Z]            | 22                                                                    | 30                                  | 47                                                                                                                        | 44                                                                           | 77                       | 90                                             |

CNT-carbon nanotube

<sup>[</sup>A] J. W. Ward, M. Meinhold, B. M. Segal, J. Berg, R. Sen, R. Sivarajan, D. K. Brock, and T. Rueckes. "A Non-Volatile Nanoelectromechanical Memory Element Utilizing A Fabric Of Carbon Nanotubes." Non-Volatile Memory Technology Symposium, 15-17 Nov. 2004, pp. 34-38. [B] T. Rueckes et al. "Carbon nanotube-Based Nonvolatile Random Access Memory for Molecular Computing." Science 289 (2000): 94-97.

<sup>[</sup>D] The projections for WRITE voltage and WRITE energy depend on the length of nanoelectromechanical element. For very small length, the operating voltage might be too high for practical use, as follows from theoretical analysis in: M. Dequesnes et al. "Calculation of Pull-In Voltages For Carbon-Nanotube-Based Nanoelectromechanical Switch." Nanotechnology 13 (2002) 120. R. Lefevre et al. "Scaling Law in Carbon Nanotube Electromechanical Devices." Phys. Rev. Lett. 95 (2005) 185504.

- [E] G. Baek, et al. "Highly Scalable Nonvolatile Resistive Memory Using Simple Binary Oxide Driven By Asymmetric Unipolar Voltage Pulses." 2004 International Electron Devices Meeting, San Francisco, CA, USA, 13/12/2004-15/12/2004, 587-90.

- [F] Estimated based on experimental data reported in Ref. [E]:  $E \sim 0.5 \text{ *V*I*} t_w$ , for V = 1 Volt, I = 0.5 mA,  $t_w = 10 \text{ ns}$ .

- [G] S. Dietrich, M. Angerbauer, M. Ivanov, D. Gogl, H. Hoenigschmid, M. Kund, C. Liaw, M. Markert, R. Symanczyk, S. Bournat, and Gerhard Mueller." A Nonvolatile 20Mbit CBRAM Memory Core Featuring Advanced Read And Program Control." IEEE J. Solid-State Circ. 42 (2007) 839. [H]  $8F^2$  for 1T1R,  $5F^2$  for 1R cells.

- [I] Estimated based on experimental data reported in Ref. [G]:  $E\sim0.5*V*I*t_w$ , for V=0.6 Volt,  $I=10\mu A$ ,  $t_w=50$  ns.

- [J] Estimated as  $E \sim 0.5 * V^2 / R_{ON} * t_w$  for V = 0.2 Volts,  $R_{ON} = 2E5$  Ohm,  $t_w = 10$  ns.

- [K] Obtained in ref. [G] from elevated temperature accelerated data retention measurements over 30 h.

- [L] M. Fujimoto et al. "Resistivity and Resistive Switching Properties of Pro., Cao., MnO., thin Films." Appl. Phys. Lett. 89 (2006) 243504.

- [M] S. T. Hsu, T. Li and N. Awaya. "Resistance Random Access Memory Switching Mechanism." J. Appl. Phys. 101 (2007) 0245517.

- [N] Y. Watanabe, J.G. Bednorz, A. Bietsch, Ch. Gerber, D. Widmer, A. Beck, S. J. Wind. "Current-driven Insulator-conductor Transition and Nonvolatile Memory in Chromium-doped SrTiO3 Single Crystals." Appl. Phys. Lett. 78, 2001, 3738.

- [O] C. Papagianni, Y. B. Nian, Y. Q. Wang, N. J. Wu, A. Igmatiev, "Impedance Study of Reproducible Switching Memory effect." 2004 International Electron Devices Meeting, San Francisco, CA, USA, 13/12/2004-15/12/2004, 125-128.

- [P] S. Liu, et al. "Electro-resistive Memory Effect in Colossal Magnetoresistive Films and Performance Enhancement by Post-annealing." Mat. Res. Soc. Symp. Proc. vol. 648 (2001) P3.26.1-8.

- [Q] Electrochemical cell potentials control the write voltage. In appropriate combinations, 0.5 V will leave some safety margin. Read voltages will be significantly smaller.

- [R] R. Muller, S. De Jonge, K. Myny, D. J. Wouters, J. Genoe, and P. Heremans. "Organic CuTCNQ integrated in complementary metal oxide semiconductor copper back end-of-line for nonvolatile memory." Appl. Phys. Lett. 89 (2006) 223501.

- [S] L. P. Ma, J. Liu, and Y. Yang. "Organic electrical bistable devices and rewritable memory cells" Appl. Phys. Lett. v. 80, no. 16 (2002) 2997-2999.

- [T] Estimated based on experimental data reported in Ref. [S]:  $E \sim 0.5 *V*I*t_w$ , for , for V = 2 Volts,  $I = 10 \,\mu\text{A}$ ,  $t_w = 10 \,\text{ns}$ .

- [U] A. DeHon, S. C. Goldstein, P. J. Kuekes, P. Lincoln. "Nonphotolithographic nanoscale memory density prospects." IEEE Trans. Nanotechnol. v. 4, no. 2 (2005) 215-228.

- [V] J. E. Green, J. W. Choi, A. Boukai, Y. Bunimovich, E. Johnston-Halperin, E. Delonno, Y. Luo, B. A. Sheriff, K. Xu, Y. S. Shin, H-R. Tseng, J. F. Stoddart, and J. R. Heath. "A 160-kilobit molecular electronic memory patterned at 1011 bits per square centimetre." Nature 445 (2007) 414.

- [W] W. Wu, G-Y. Jung, D. L. Olynick, J. Straznicky, Z. Li, X. Li, D. A. A. Ohlberg, Y. Chen, S-Y. Wang, J. A. Liddle, W. M. Tong, and R. S. Williams, "One-kilobit cross-bar molecular memory circuits at 30-nm half-pitch fabricated by nanoimprint lithography," Appl. Phys. A v. 80 (2005) 1173-1178. [X] Chen Y., Ohlberg D.A.A., Li XM, Stewart D.R., Williams R.S., Jeppesen J.O., Nielsen K.A., Stoddart J.F., Olynick D.L., Anderson E.. "Nanoscale Molecular-switch Devices Fabricated by Imprint Lithography." Appl. Phys. Lett 82 (2003) 1610.

- [Y] V. Meunier, S. V. Kalinin, and B. G. Sumpter, "Nonvolatile memory elements based on the intercalation of organic molecules inside carbon nanotubes." Phys. Rev. Lett. 98 (2007) 056401.

- [Z] The number of referred articles in technical journals that appeared in the Science Citation Index database for 7/1/2005–7/1/2007.

#### メモリデバイス ― 掲載したメモリの定義と議論

A. 容量ベース型 (表 ERD5a)

トンネル障壁エンジニアリングメモリ ― トンネル障壁エンジニアリングメモリは、基本的には浮遊ゲートメモ リの構造と同じであるが、書込み/消去特性を向上するために傾斜障壁あるいは多層構造の絶縁障壁膜を 用いている。傾斜(たとえば鶏冠状)障壁の浮遊ゲートメモリ1,2は、記憶ノードへの、あるいは記憶ノードから の効果的なトンネリングを可能にする特殊な障壁形状を得るために、種々の絶縁膜を積層して用いる。この コンセプトは非常に魅力的であるが、積層した誘電体膜を用いて傾斜バンドギャップ・トンネル障壁を作製す ることは、その実現が極めて難しい。実現には、傾斜バンドギャップや傾斜誘電率を持つ新しい誘雷体材料 が必要となる。傾斜バンドギャップ誘電体材料のコンセプトは、傾斜バンドギャップを持つⅢ-Ⅴへテロ構造 に似ている。傾斜電荷注入障壁³は前述の傾斜注入障壁メモリのコンセプトの前身として実験的に実証され ているが、これを作製するために傾斜 Al<sub>x</sub>Ga<sub>1-x</sub>As/GaAs 構造が使われたことは特記に値する。鶏冠状トンネ ル障壁積層構造 Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>が実験的に検討され、その不揮発性メモリ特性が改善することが報告され ている4。また、傾斜トンネル障壁の候補となり得るAlOx及びHfO25,6膜についての最近の研究がある。

VARIOT(<u>vari</u>arable oxide thickness floating gate memory)メモリ<sup>7,8</sup>では、誘電率が異なる2つの誘雷体の積 層膜が用いられている。この構造は、比較的低い供給電圧で高いトンネル電流を得ることができるとともに、 データ保持特性にも優れている。トンネル障壁エンジニアリングは、メモリセルのプログラムと消去に必要な 電圧を低減する効果がある。SiO2と HfO2 あるいは Al2O3 の積層構造が検討されており、トンネルによるより 低電圧でのプログラミングと10年間のデータ保持が実証されている。

トンネル障壁エンジニアリングメモリの他のコンセプトに、バンドギャップ調整型の SONOS メモリ $^9$ (BESONOS)がある。トンネル酸化膜の代わりに極薄の SiO $_2$ /Si $_3$ N $_4$ /SiO $_2$ 障壁を用い、消去と保存のモード間に必要な非対称性を生み出している。

強誘電体 FET メモリ — 従来の 1T1C 強誘電体 RAM(FeRAM)は、DRAM セルのキャパシタに溜められる電荷と同程度の反転可能な分極電荷を必要とする。必要な電荷量を確保するためには、3 次元的に畳み込まれた強誘電体キャパシタが必要となり、そのキャパシタが占める面積のためにスケーラビリティーが制限される。それに比べて、もし強誘電体キャパシタを FET のゲート積層構造の中に組み込めれば、強誘電体の分極は直接、チャネル中の電荷に作用でき、FET の入力特性の明確な変化を起こすことができる。この 1T メモリデバイスは、強誘電体 FET(FeFET)<sup>10</sup>と呼ばれる。チャネル界面における低い界面準位密度を保証するためには、高品質の絶縁膜が必要となる。それ故、このデバイスの現実的なゲート構造は、金属-強誘電体-絶縁体-半導体(MFMIS)の積層構造となる。強誘電体と絶縁体の間に別の金属が挿入されることもある(MFMIS)。FeFET デバイスは、MOSFET としてのスケーラビリティーを持つ。しかし、スケーリングは 22 nm程度が限界であろう。これ以上縮小すると、絶縁膜厚が薄くなり過ぎて、抗電界の膜厚依存性から考えて強誘電的性質を維持するのが困難になるからである<sup>11</sup>。この 10 年間で、FeFET ベースの不揮発性メモリを作製する多くの試みがなされた。最も大きな課題は、強誘電体・半導体の界面に関する長期信頼性である。最近、保持時間に対する著しい改善が報告された<sup>12,13</sup>。疲労や焼き付きといった他の信頼性問題は、まだ十分に研究・理解されていない。

#### B. 抵抗ベース型 (表 ERD5b)

抵抗ベース型メモリは、ナノ電気機械式メモリと金属-絶縁体-金属(MIM)システム群からなり、電気パルス誘起の抵抗変化効果を示す。MIMシステムにおける考え得る抵抗スイッチングのメカニズムは、物理的及び/または化学的効果の組み合わせからなることが多い。そのメカニズムは、熱的効果、イオン的効果、あるいは電気的効果のうち、支配的な寄与をしているものによりグループ分けできる<sup>14</sup>。この節では、まずナノ電気機械式メモリについて議論し、続いて3種類の金属-絶縁体-金属システムについて議論する。

ナノ電気機械式メモリ(NEMM)— NEMM は、双安定な極小の電気機械式スイッチに基づいている。このコンセプトにおいて機械的なデジタル信号は、電気回路の開閉を引き起こす固体の極小要素(たとえば、ナノ細線、極小円柱、あるいはナノ粒子)の変位によって表される。NEMM の最初のコンセプトは、カーボンナノチューブ(CNT)を用いた立体交差型のメモリである<sup>15</sup>。各メモリ要素は、宙吊りに渡された CNT を基にしている。CNT の立体交差によって作ったアレイ(配列)構造では、各交差箇所に、機械的に双安定で静電気的にスイッチできるデバイス要素が形成される。メモリの状態は、接合(交差箇所)の抵抗値として読み出される。NEMM から派生した複数の提案が現在、検討されている。たとえば、CNT ブリッジ<sup>16</sup>、CNT カンチレバー(片持ち梁)<sup>17</sup>、そしてシリコンのカンチレバー<sup>18</sup>などである。最近、極微(ナノ)結晶シリコン(nc-Si)ドットを組み込んだ極小の電気機械式デバイスが提案されている<sup>19</sup>。nc-Si ドットは、MOSFET 構造の中に形成された機械的に双安定な浮遊ゲートの中に、電荷蓄積中心として埋め込まれている。不揮発性 RAM に加え、極小の電気機械式シフトレジスタ・メモリが最近、提案されている<sup>20</sup>。NEMM の大きな課題の一つは、高集積メモリアレイの確実な作製であり、CNT の特性制御の困難さのような材料や作製上の問題点が絡んでいる。

**単極のヒューズ/反ヒューズ型メモリ** — 熱的効果による MIM 構造における特有の抵抗スイッチング現象は、明らかに単極的性質を持つ。この現象は、電圧誘起による局所的な絶縁破壊によって引き起こされ、このとき、放電フィラメント中の物質はジュール熱により著しく変質する。電流コンプライアンスにより、制御された抵抗値を持つ脆弱な導電性のフィラメントのみが形成される。このフィラメントは、絶縁体中へ移動した電極金属、残存有機物の炭素<sup>21</sup>、あるいは、半酸化物のような分解された絶縁材料<sup>22</sup>からなると思われる。リセット過程において、この導電性フィラメントは、局所的に生成される 10<sup>12</sup> W/cm³ 台の高い電力密度により再び熱分解される。このメカニズムは、ヒューズ・反ヒューズ型と言われている。提案された多くの候補の一つがNiO であり、1960 年代に最初の報告がある<sup>23</sup>。最近、NiO<sup>24</sup>及び TiO<sub>2</sub><sup>25</sup>に対して、ON 状態における導電性経

路のフィラメント的性質が確認されている。Pt/NiO/Pt 薄膜のセルが CMOS 技術の中に無理なく組み込まれ て、不揮発性メモリ動作が実証されている26。単極的スイッチング効果における重要なパラメータの一つは、 現象発現に必要な電流値であろう。単極的抵抗スイッチングにおいては熱的効果が支配的と思われがちだ が、一方、電気化学的プロセスも何らかの役割を果たしている27,28,29との示唆があることも忘れてはならない。 銅酸化物の抵抗スイッチングに関する最近の研究では、非常に強い電極依存性が示されている<sup>30</sup>。このタイ プのメモリでは、スイッチング電流、従って書込みエネルギーが相対的に高くなる。また、メモリのスイッチング パラメータのばらつきが相対的に大きいことも問題である。スイッチング電流密度を低減したという報告があり <sup>31</sup>、また、NiO と電極の間に薄い IrO。層を挟むことで、メモリのスイッチングに関するすべてのパラメータのば らつきが最小化されている<sup>32</sup>。

イオン移動メモリ ― メモリ動作は、電極材料か絶縁材料あるいは両方における酸化還元プロセスに基づ いている。絶縁材は、イオン伝導性を示すことが求められる。材料としては、酸化物、高次のカルコゲナイド (ガラスを含む)、半導体の他、高分子を含む有機化合物が挙げられる。一つのやり方は、陽イオン輸送と陰 極での還元、それによる金属フィラメントの成長に基づくものである。主として Ag と Cu ベースのシステムで、 試作セルの動作に成功している33,34。フィラメントが形成され対向電極がつながると低抵抗状態となり、一方、 酸化反応によりフィラメントが分解すると高抵抗状態に戻る。他のやり方では、絶縁材料自体に電気伝導性 を誘起する陰イオン(たとえば酸素イオン)輸送と酸化還元反応を利用する35,36。多くの場合、双安定スイッチ ングを起こすためには、事前に何らかの発現プロセスが必要となる。このメモリの電気伝導は、しばしばフィラ メント的性質を示す。もし、それを制御できれば、この双安定スイッチング過程に基づくメモリは、微細化にお いて非常に小さな特性長まで対応できる。スイッチング速度は、イオン輸送によって制限される。酸化還元制 御による双安定スイッチングに関係する活性距離が小さい場合(10 nm以下)、スイッチング時間は 2-3 ns に できる。報告された各種現象のメカニズムの詳細がまだ不明であるため、各種特性の正確な予想はまだ困難 である。

電子効果メモリ — 電子効果メモリは、3 つの異なるメカニズムを含む:1) 電荷注入と捕獲、2) モット転移、 3) 強誘電体分極効果:

- 1. 電荷の注入と捕獲は、抵抗変化の原因となり得る。電荷捕獲モデル(Simmons-Verderber 理論<sup>37</sup>)によ れば、電荷は高電界において Fowler-Nordheim トンネリングによって注入され、ついで絶縁体中の欠陥 や金属ナノ粒子のようなサイトに捕獲される。この過程は MIM 構造の静電障壁特性を変化させ、従って 構造の抵抗値も変化させる。修正モデルでは、界面状態における捕獲が議論されている。この捕獲は、 様々な金属/半導体性ペロブスカイトの界面において、隣接するショットキー障壁に影響を及ぼす38,39。 別の例として、Si の極細線のメモリがある。多結晶 Si の極細線の抵抗は、細線中の結晶粒界に捕獲さ れた少数の電荷によって調整される<sup>40,41</sup>。この方式は再現性に乏しい問題があるが、一方、バルクの MOSFET をなくせるのでセルサイズを著しく低減できる。この Si 極細線に基づいた 128 Mbit のメモリが、 実際に作られている42。さらなる検討が必要な材料の問題点として、繰り返しに対する脆弱性―スイッチ の繰り返しにおける欠陥形成一がある。欠陥密度分布は統計的な不確実さをもつため、欠陥形成により、 寿命とサイズ縮小の両方が制限されることが懸念される43。

- 2. モット転移メモリでは、電荷の注入は強相関電子から弱相関電子への転移を誘起し、その結果、絶縁 体 - 金属転移を引き起こす。モット転移のメカニズムは、(Pr,Ca)MnO<sub>3</sub>(PCMO),44,45,46 SrTiO<sub>3</sub>:Cr,47 Ag/CeO2/LCMO ヘテロ構造48のようなペロブスカイト型酸化物に対して報告されている。モット転移による 抵抗スイッチングが、Pt/TiO<sub>2</sub>/TiN/Pt システムに対して最近、報告されている<sup>49,50</sup>。このタイプのデバイス の重要な課題の一つは、各種パラメータ(電荷密度、歪み、結晶の乱れ、局所的な組成など)の小さな変 化に対する相関電子の応答感度である51。それ故、材料と界面の物理的及び化学的構造の精密な制御 が、極めて重要となる。

3. 強誘電体分極は、極薄膜のトンネル特性、あるいは、隣リ合った半導体層におけるショットキー型空間 電荷層を変調することができ<sup>52,53</sup>、これにより強誘電性の抵抗スイッチングが生じる。今のところ、観察されたスイッチング現象の原因が強誘電的なものであるとの確証はない。

高分子メモリ — 高分子メモリは、ポリマー(重合体)あるいは有機メモリとも呼ばれるが、金属成分が埋め込まれた有機物の薄膜で作られたメモリ要素から成る。埋め込まれた金属成分は、薄い金属層やナノサイズ金属粒の集団 $^{54,55,56,57,58}$ 、あるいは有機金属材料 CuTCNQ と AgTCNQ (TCNQ=7,7,8,8-tetracyano-pquinodimethane)中の金属イオンなどである $^{59}$ 。ポリマーの膜中に埋め込まれた  $C_{60}$ 分子に基づくメモリデバイスも最近、報告されている $^{60}$ 。これらすべての構造は、同じ印加電圧に対して、伝導率が異なる 2 つの状態を示す。書込み操作は、この構造への電圧パルス印加で行われ、これにより低抵抗と高抵抗状態間の可逆的なスイッチングが行われる。状態転移後は、電源を切っても、2 つの状態のうちの一つが維持される。消去操作は、逆電圧のパルス印加で行われる。

実験結果によれば、埋め込み金属層は、高分子メモリ素子の双安定 I-V 特性において重要な役割を果たしているようである<sup>61</sup>。メモリ動作原理は、まだ、明らかでない。ヒューズ/反ヒューズあるいはイオン伝導メモリにおけるような、導電性フィラメントの形成は関係していないようである。複数の研究者<sup>62</sup>が、双安定性のメカニズムは Simmons-Verderber 理論<sup>63</sup>によって説明できるとしている。この場合、抵抗変化は離散した金属ナノ結晶における電荷の捕獲によって生じており、従ってこのタイプのメモリは電子効果メモリの範疇に入ることとなる。

分子メモリー 分子メモリは、単一分子をメモリセルの構成要素として使う様々な提案の総称であり、情報の1 bit は分子一つの空間に保存される。実験的に動作を実証した一つの方法は、2 つの電極間に分子を取り付け、電圧印加による制御で実効コンダクタンスの高速な可逆変化を起こすというものである<sup>64,65,66,67</sup>。この分子メモリでは、外部電圧の印加により分子を 2 つの可能な伝導状態のうちの一つへ転移させることで、データが保存される。データは、分子セルの抵抗変化を測定することで読み取られる。DRAM<sup>68</sup>や浮遊ゲートメモリのような現状のメモリ技術の中に、分子を構成要素として取り込むという構想もある。分子における伝導率スイッチングのメカニズムは、まだ完全には理解されていない。初期に報告された実験結果のいくつかは、分子を通じた電子輸送は 2 つの金属電極間に取り付けられた分子に沿った金属フィラメントの形成によるとしている <sup>69</sup>。それ故、分子スイッチの本来の性質は、往々にして他の効果によって遮蔽されている可能性がある。次のステップ、すなわち、機能的に活性な分子どうしの分子による接続は、長期的な研究が必要になると見られている。分子エレクトロニクスに対する知識基盤の確立には、さらなる基礎的な研究が必要である。

#### ロジック及び代替え情報処理デバイス

過去3版のこの節では、代替ロジック技術に、高機能汎用演算においてCMOSデバイスを置き換える可 能性があるか、ということに関して議論された。その結果、そこで調査された代替技術には、今後十年間は、 ITRS ロードマップ上に記載された CMOS デバイスを置き換える可能性はないことが分かった。このため、全 世界における代替技術の膨大な研究の中で、新しい技術の際立った物理的特徴が、CMOS に比べて優れ、 CMOSと結合でき、汎用ブール代数論理以外のなんらかの有用な情報処理機能が存在しうるかどうか、とい う疑問が投げかけられた。この版の Emerging Research Device の章では、このことおよびそれに関連した疑 間に言及する。

また、ERDの章の以前の節と同じく、本節にも推移表を持ち、それを Table ERD6 として示す。推移 Table は、2005年版から2007年版に進むにつれて、Table ERD7aに加わる、および、抜ける技術を示す。また、 2009年版に加えられる可能性のある4つの新しい技術も示す。

非ブール代数論理に向けた代替デバイスの予想される性能の解析は、本質的に、それに伴うアーキテク チャに関係する。Emerging Research Architecture の節に示されるように、ヘテロで非対称なマルチコアプロ セッサを志向する現在の産業トレンドは、今後のシステムが、特殊用途向けの新しいデバイスを利用する専 用コプロセッサをサポートするという考えと整合している。こうした専用コプロセッサおよびアクセラレータは一 つあるいはそれ以上のコアとして集積され、CMOS をベースとした従来の汎用システムの中で、特殊な演算 に用いられる。その一例として、画像認識あるいはスピーチ認識用コプロセッサ、データ検索のための Bavesian 干渉エンジン、合成を応用とした連想メモリユニットなどがある。